# apitech Model # 15313

# Nuclear Event Detector (NED) Data Sheet

A Nuclear Event Detector (NED) is an essential element of any nuclear hardened electronic system hardware. It provides sensing and response signals to ionizing radiation pulses emitted during nuclear events.

Under such conditions, the NED, with a customer programmed threshold (external resistor) will provide two outputs:

- A timed output (set by an external capacitor)

- A latched output with electrical reset

The module is supplied in a 14 pin military standard hermetic package that is fully tested and compliant with military requirements. It is capable of detecting short duration pulses and has a number of features including a test input to verify functional health.

# Features

- Detection of ionising radiation above a pre-set level

- Ability to set a trigger threshold by a single external resistor (RTH)

- Provision of a fast pulsed detected output (NED)

- Ability to set the NED output pulse duration by a single external capacitor (CA to CB)

- Provision of a fast latched flag output ( $\overline{\text{NEF}}$ )

- Provision of complementary flag reset inputs (FR and FR)

- Provision of a separate supply for the main electronics (VH)

- Provision of a separate bias supply for the detection diode (VB)

- Provision of a separate load supply for the output drive transistors (VL)

- Operation within specification across the military temperature range (-55°C to +125°C)

# **Maximum Ratings**

| Parameter                                                  | Limit                   |

|------------------------------------------------------------|-------------------------|

| Voltage at pins 6, 11, 12 and 14 w.r.t. pin 7              | 7.0 V                   |

| Voltage at pin 1 w.r.t. pin 7                              | 20 V                    |

| Voltage at pin 8 w.r.t. pin 7                              | 5.5 V                   |

| Storage temperature range                                  | -65°C < Ta < +150°C     |

| Ionising radiation dose rate (operate through and survive) | >1E8 Gy(Si)/s           |

| Ionising total dose                                        | >100 Gy(Si)             |

| Neutron fluence                                            | >1E13 n/cm <sup>2</sup> |

# **Table 1 Pin Description**

| Pin | Name            | Function | Description                              |  |

|-----|-----------------|----------|------------------------------------------|--|

| 1   | VL              | SUPPLY   | Output pull-up supply                    |  |

| 2   | NED             | OUTPUT   | Nuclear Event Detector pulsed output     |  |

| 3   | NC3             | n/c      |                                          |  |

| 4   | C <sub>B</sub>  | INPUT    | Timing capacitor (negative)              |  |

| 5   | C <sub>A</sub>  | OUTPUT   | Timing capacitor (positive)              |  |

| 6   | TEST            | INPUT    | Built in Test input                      |  |

| 7   | GND             | GROUND   | Device supply ground and case connection |  |

| 8   | V <sub>B</sub>  | SUPPLY   | Device detector bias supply              |  |

| 9   | R <sub>TH</sub> | INPUT    | Threshold set input                      |  |

| 10  | NC10            | n/c      |                                          |  |

| 11  | NFR             | INPUT    | Flag reset inverse input                 |  |

| 12  | FR              | INPUT    | Flag reset input                         |  |

| 13  | NEF             | OUTPUT   | Nuclear Event Flag output                |  |

| 14  | V <sub>H</sub>  | SUPPLY   | Device Supply                            |  |

#### TRIGGER THRESHOLD SETTING

The NED has provision for setting a nominal trigger threshold between 1E3 & 1E6 Gy(Si)/s using a single external resistor. The threshold is a product of the resistor value (Fig. 2) and radiation pulse width (Fig. 3). The following equation can be used :-

$$DR = \frac{2.18E7}{Rth/(1 - e^{\left(-\frac{125tp}{Rth}\right)})}$$

DR= radiation pulse amplitude in Gy/s Rth = resistor value tp = rectangular radiation pulse width in ns 1 Gy/s = 100 rad/s

### *NED* PULSE DURATION SETTING

The duration of the  $\overline{\text{NED}}$  pulse width is set by an external capacitor connected between the Ca and Cb pins. The nominal calculation is 20us/nF.

The pulse width should be set long enough to protect the system from the initial event until radiation has fallen to safe levels at which the system can operate.

# TABLE 2. Electrical performance characteristics

| Parameter                                                        | Symbol              | Conditions -55°C 2 T <sub>A</sub> 22+125°C                                                                                                                                                                           | Limits |      |      | Unit  |

|------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|

|                                                                  |                     | unless otherwise specified                                                                                                                                                                                           | Min    | Тур  | Max  |       |

| Standby Supply Current                                           | Ι <sub>Η</sub>      | $\label{eq:supply voltage V_H = 5.5V, TEST Input = 0.00V to 0.05V, \\ \mbox{NFR Input = 4.5V to 5.5V, FR Input = 0.00V to 0.05V,} \\ \hline \mbox{NED and } \hline \mbox{NEF outputs high (>4.5V)} \\ \end{tabular}$ |        |      | 2.0  | mA    |

| Flag Set Supply Current                                          | I <sub>H</sub>      | $V_{H}$ = 5.5V, $\overline{\text{NED}}$ output >4.5V, $\overline{\text{NEF}}$ output <0.5V                                                                                                                           |        |      | 6.0  | mA    |

| Operational Supply Current                                       | I <sub>H</sub>      | $V_{H}$ = 5.5V, $\overline{\text{NED}}$ and $\overline{\text{NEF}}$ outputs <0.5V                                                                                                                                    |        |      | 15.0 | mA    |

| Output Leakage Current                                           | IL.                 | VL = 20.0V, $\overline{\text{NED}}$ and $\overline{\text{NEF}}$ outputs >4.5V                                                                                                                                        |        |      | 100  | uA    |

| Detector Leakage Current                                         | IB                  | Detector bias voltage V <sub>B</sub> = 5.5V, $\overline{\text{NED}}$ output >4.5V, $\overline{\text{NEF}}$ output <0.5V                                                                                              |        |      | 5.0  | uA    |

| Detector Forward Voltage                                         | V <sub>F</sub>      | Forward current, I <sub>TH</sub> = 10mA                                                                                                                                                                              | 0.25   |      | 1.0  | V     |

| FR Input Current                                                 | I <sub>FR</sub>     | Flag reset voltage $V_{FR}$ = 0.7V, $R_{TH}$ not connected (note 6)                                                                                                                                                  |        | 0.5  | 1.0  | mA    |

|                                                                  | I <sub>FR</sub>     | Flag reset voltage $V_{FR}$ = 3.0V, $R_{TH}$ not connected (note 6)                                                                                                                                                  |        | 2.3  | 3.0  | mA    |

| FR Switching Voltage                                             | V <sub>FRSW</sub>   | R <sub>TH</sub> not connected (note 6)                                                                                                                                                                               | 0.7    | 2.1  | 3.0  | V     |

| FR Input Current                                                 | I <sub>NFR</sub>    | $\overline{\mathrm{FR}}$ voltage V <sub>NFR</sub> = 0.7V, R <sub>TH</sub> not connected (note 6)                                                                                                                     |        | -0.5 | -3.0 | mA    |

|                                                                  | I <sub>NFR</sub>    | $\overline{\mathrm{FR}}$ voltage V <sub>NFR</sub> = 4.0V, R <sub>TH</sub> not connected (note 6)                                                                                                                     |        | -0.1 | -1.0 | mA    |

| FR Switching Voltage                                             | V <sub>NFRSW</sub>  | R <sub>TH</sub> not connected (note 6)                                                                                                                                                                               | 0.7    | 1.6  | 2.0  | V     |

| TEST Input Current                                               | I <sub>TEST</sub>   | TEST voltage V <sub>TEST</sub> = 0.7V                                                                                                                                                                                |        | 0.5  | 1.0  | mA    |

|                                                                  | I <sub>TEST</sub>   | TEST voltage V <sub>TEST</sub> = 4.0V                                                                                                                                                                                |        | 3.3  | 4.0  | mA    |

| TEST Switching Voltage                                           | V <sub>TESTSW</sub> |                                                                                                                                                                                                                      | 0.7    | 2.1  | 3.0  | V     |

| NED Output Voltage                                               | V <sub>DOH</sub>    | $V_L = 20V$ , $\overline{\text{NED}}$ output current $I_0 = -100\mathbb{P}A$                                                                                                                                         | 18.5   |      |      | V     |

|                                                                  | V <sub>DOL</sub>    | $\overline{\text{NED}}$ output current I <sub>OL</sub> = 10mA                                                                                                                                                        |        |      | 0.6  | V     |

|                                                                  | V <sub>DOL</sub>    | $\overline{\text{NED}}$ output current I <sub>OL</sub> = 20mA                                                                                                                                                        |        |      | 0.7  | V     |

| NEF Output Voltage                                               | V <sub>FOH</sub>    | $V_L = 20V$ , $\overline{\text{NEF}}$ output current $I_O = -100\mathbb{P}A$                                                                                                                                         | 18.5   |      |      | V     |

|                                                                  | V <sub>FOL</sub>    | $\overline{\text{NEF}}$ output current I <sub>OL</sub> = 10mA                                                                                                                                                        |        |      | 0.6  | V     |

|                                                                  | V <sub>FOL</sub>    | $\overline{\text{NEF}}$ output current I <sub>OL</sub> = 20mA                                                                                                                                                        |        |      | 0.7  | V     |

| TEST Input pulse width                                           | t <sub>TEST</sub>   | V <sub>TEST</sub> = 0V to 4.0V                                                                                                                                                                                       | 250    |      |      | ns    |

| TEST to $\overline{\text{NED}}$ or $\overline{\text{NEF}}$ delay | to                  | V <sub>TEST</sub> = 0V to 4.0V duration 10⊡s                                                                                                                                                                         |        | 5    | 10   | us    |

| FR Input pulse width                                             | t <sub>FR</sub>     | $V_{FR} = 0V$ to 4.0V                                                                                                                                                                                                | 250    |      |      | ns    |

| FR Input to $\overline{\mathrm{NEF}}$ Delay                      | tr                  | V <sub>FR</sub> = 0V to 4.0V duration 12s                                                                                                                                                                            |        | 0.2  | 1.0  | us    |

| FR Input pulse width                                             | t <sub>NFR</sub>    | V <sub>NFR</sub> = 5.0V to 0.7V                                                                                                                                                                                      | 500    |      |      | ns    |

| $\overline{FR}$ Input to $\overline{NEF}$ delay                  | ts                  | V <sub>NFR</sub> = 5.0V to 0.7V duration 1 <sup>2</sup> / <sub>1</sub> s                                                                                                                                             |        | 0.25 | 1.0  | ₽S    |

| NED Output Delay                                                 | tt                  | $V_{RTH}$ = 0V to 5.0V duration 100ns, pull-up resistor =220 $\Omega$                                                                                                                                                |        | 25   | 50   | ns    |

| NEF Output Delay                                                 | tu                  | $V_{RTH}$ = 0V to 5.0V duration 100ns, pull-up resistor =220 $\Omega$                                                                                                                                                |        | 50   | 200  | ns    |

| $\overline{\text{NED}}$ output pulse width                       | t <sub>NED</sub>    | Supply voltage $V_H$ = 4.5V to 5.5V, pulse duration timed from negative edge of TEST input                                                                                                                           | 10     | 20   | 30   | us/nF |

| NED Output Pulse Width                                           | t <sub>NED</sub>    | Supply voltage V <sub>H</sub> = 4.95V to 5.05V                                                                                                                                                                       | 13     | 20   | 27   | ⊡s/nF |

Footnotes for Table 2:

- 1. All voltage measurements are made with respect to pin 7 (GND) unless otherwise stated.

- 2. The definition of low and high voltage levels are:  $V_{OL} < 0.5V$ ,  $V_{OH} > 4.5V$  unless otherwise stated.

Т

- 3.  $V_L$  and  $V_H$  = 4.5V to 5.5V unless otherwise stated.

- 4.  $V_{B}$ ,  $\overline{NED}$  and  $\overline{NEF}$  are not connected unless otherwise stated.

- 5.  $C_T = 47nF + /-10\%$  and connected to pins 4 and 5 unless otherwise stated.

- 6.  $R_{TH} = 180^{\circ} + / -2^{\circ}$  connected between pin 9 (RTH) and pin 7 (GND) unless otherwise stated.

- 7. In standby mode (no nuclear event detected) both NED and NEF outputs and NFR input will be in the 'high' state and TEST and FR input will be in the 'low' state.

# TABLE 3. Truth Table

|                                               |      |    | Time - | t = 0s | t = 0s | After | After | After | After | After |

|-----------------------------------------------|------|----|--------|--------|--------|-------|-------|-------|-------|-------|

|                                               |      |    | ?      |        |        | to    | tq    | tp    | tp    | tr    |

| STATUS                                        | TEST | FR | FR     | NED    | NEF    | NED   | NEF   | NED   | NEF   | NEF   |

| Standby                                       | L    | Н  | L      | Н      | Н      | Н     | Н     | Н     | Н     | Н     |

| Nuclear event detection<br>(or simulation)    | Н    | Н  | L      | Н      | Н      | L     | Ĺ     | Н     | L     | Н     |

| After nuclear event detection (or simulation) | L    | Н  | L      | L      | L      | L     | L     | Н     | L     | Н     |

| Reset by FR input                             | L    | Н  | Н      | Н      | L      | N/A   | N/A   | N/A   | N/A   | Н     |

| Reset by NFR input                            | L    | L  | L      | Н      | L      | N/A   | N/A   | N/A   | N/A   | Н     |

Footnotes for Table 2:

- 1. Time  $t_0$  is the delay between the TEST input voltage rising to 90% of its peak voltage and the NED output falling to 10% of its peak voltage.

- 2. Time t<sub>p</sub> is the width of the pulse from the NED output measured between the falling and rising edges at 50% of the amplitude.

- Time t<sub>q</sub> is the delay between the TEST input voltage rising to 90% of its peak voltage and the NEF output falling to 10% of its peak voltage.

- 4. Time t<sub>r</sub> is the delay between the FR input voltage rising to 90% of its peak voltage and the NEF output rising to 90% of its peak voltage.

- Time t<sub>s</sub> is the delay between the NFR input voltage falling to 10% of its peak voltage and the NEF output rising to 90% of its peak voltage.

- 6. Outputs inactive during power up provided  $V_H$  rises at < 5000 V/s (5 V/ms)

#### PART ORDERING INFORMATION

| Part Number     | Feature                              | Option                      |

|-----------------|--------------------------------------|-----------------------------|

| 5962-1022001HXC | 14 pin DIL as per DLA SMD 5962-10220 | gold plate finish leads     |

| 5962-1022001HXA | 14 pin DIL as per DLA SMD 5962-10220 | hot solder dip finish leads |

| 15313           | 14 pin DIL case outline              | gold plate finish leads     |

| 15313A          | 14 pin DIL case outline              | hot solder dip finish leads |

| 14907           | 14 pin flatpack case outline         | gold plate finish leads     |

| 14907A          | 14 pin flatpack case outline         | hot solder dip finish leads |

|                 |                                      |                             |

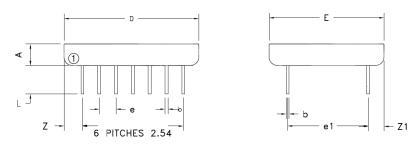

# Figure 2. DIL Case Outline

| DEE | DI    | MENSIONS | mm    | DIMENSIONS in |       |       |  |

|-----|-------|----------|-------|---------------|-------|-------|--|

| REF | MIN   | NOM      | MAX   | MIN           | МАХ   |       |  |

| D   | 20.06 | 20.19    | 20.32 | 0.790         | 0.795 | 0.800 |  |

| Е   | 12.44 | 12.57    | 12.70 | 0.490         | 0.495 | 0.500 |  |

| А   | _     | 3.56     | 3.69  | _             | 0.140 | 0.145 |  |

| L   | 4.95  | 5.08     | 5.21  | 0.195         | 0.200 | 0.205 |  |

| b   | -     | 0.46     | -     | _             | 0.018 | -     |  |

| е   | -     | 2.54     | -     | _             | 0.100 | _     |  |

| e1  | _     | 7.62     | -     | _             | 0.300 | _     |  |

| Z   | -     | 2.46     | -     | -             | 0.097 | -     |  |

| Z1  | -     | 2.46     | -     | _             | 0.097 | -     |  |

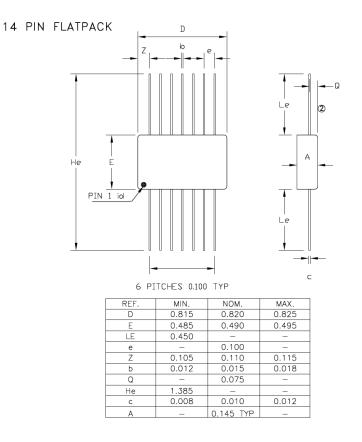

# Figure 3. FP Case Outline