# 8 Watt Hybrid Driver Amplifier

2.0 – 6.0 GHz, 4 Watt Hybrid Driver Amplifier

### **Features**

- High Saturated Output Power to 10 Watts

- Rugged GaN Technology

- Balanced Output Configuration for Optimum Return Loss

- 2 Stage Amplifier with Independent Gate & Drain Bias Controls

- Small Laser Sealed Housing

- Drop-in with Pins for Direct PCB Launch

API Technologies' Model QB-925 is a class AB driver amplifier utilizing the latest in GaN die technology to provide rugged broadband performance over the 2.4 to 6.0 GHz frequency range. The 2 stage discrete hybrid design consists of an input driver and a balanced final with independent gate and drain controls to allow for external optimization of bias settings.

At a nominal DC input voltage of +28V, the QB-925 offers a typical small signal gain of 21 dB and is capable of providing a saturated output power of 10W with an input level of approximately +24 dBm. This GaN hybrid design with its balanced configuration and laser sealed housing can withstand severe load mismatches at full rated power under adverse environmental conditions.

| Characteristic                           |                | Typical   | Min / Max   |

|------------------------------------------|----------------|-----------|-------------|

| Frequency (GHz)                          |                | 2.0 - 6.0 | 2.4 - 6.0   |

| Gain (dB)                                |                | 20        | 18 / 22     |

| Gain Variation Over Temp (dB)            |                | ± 1.5     | _           |

| Gain Flatness (dB)                       |                | ± 1.0     | ± 2.0 Max.  |

| Reverse Isolation (dB)                   |                | 52        | 45 Min.     |

| VSWR                                     | Input          | 4.5 :1    | _           |

|                                          | Output         | 1.3 :1    | 2.0 :1 Max. |

| Output Power @<br>3 dB Compression (dBm) |                | +40       | +37 Min.    |

| Noise figure (dB)                        |                | 3.0       | 5.0 Max.    |

| Power                                    | Vdc            | +28       | +22 to +30  |

|                                          | mA (Quiescent) | 330       | -           |

# **Technical Specifications (25°C)**

# Maximum Ratings (25°C)

| Operating Case Temperature               | -40ºC to +85ºC  |

|------------------------------------------|-----------------|

| Storage Temperature                      | -55ºC to +125ºC |

| Gate Threshold Voltage (V <sub>G</sub> ) | -8 Vdc Min.     |

| Drain Voltage (V <sub>D</sub> )          | +32 Vdc         |

| RF Input Drive Level                     | +30 dBm         |

#### Notes:

- 1. Specifications are based on measurements in a 50 Ohm system with a nominal DC power of +28V applied to both drains.

- For each stage, the gate voltage must be sequenced ON before applying the respective drain voltage to prevent damage to the unit. Refer to the section on Bias Sequencing for details.

Page #1

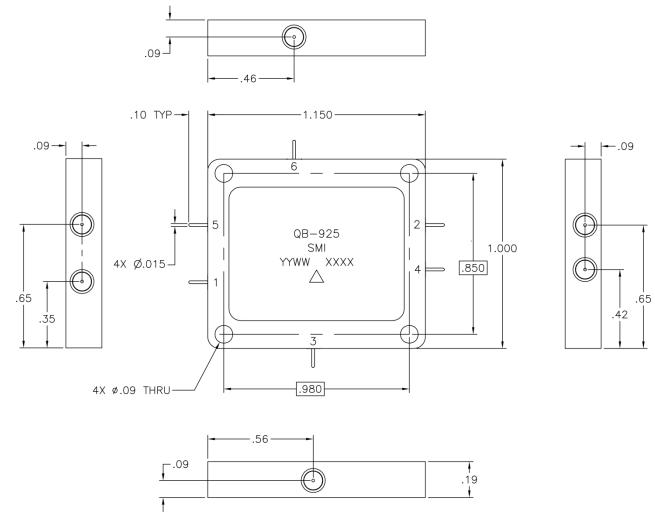

# **Outline Drawing**

### **Pin Function**

| 1 | RF Input            |

|---|---------------------|

| 2 | RF Output           |

| 3 | V <sub>DRAIN1</sub> |

| 4 | V <sub>DRAIN2</sub> |

| 5 | V <sub>GATE1</sub>  |

| 6 | V <sub>GATE2</sub>  |

Rev Date: 2/11/2014

Page # 2 © API Technologies Corp. Proprietary Information www.apitech.com micro.apitech.com | +1.888.553.7531 | MicrowaveSales@apitech.com

Page # 3

### **Bias Sequencing**

### NOTES:

- 1. Mount the QB-925 in the evaluation test fixture, or to an adequate heat sink prior to applying DC power.

- 2. Use the following Bias Adjustment procedure to properly sequence the positive and negative power supplies to prevent transistor failure or degradation.

- 3. With the gate voltages initially set at -4.0 Vdc, the DUT should not draw DC current.

- 4. Do not exceed a minimum gate voltage of -8.0 Vdc to avoid damage to the Gate-to-Source junction on the RF transistors.

- Important: The drain voltage should never be connected to the unit, or sequenced ON, before applying the gate voltages.

### ADJUSTMENT PROCEDURE:

1. Initial power supply settings:

V<sub>GATE (1)</sub> & V<sub>GATE (2)</sub> = -4.0 Vdc

$V_{\text{DRAIN}(1)} \& V_{\text{DRAIN}(2)} = +28 \text{ Vdc}$

Note: The drain voltages can be connected to the same power supply. Limit the current on the supply to 500 mA.

- 2. Connect  $V_{GATE (1)}$  to J5 and  $V_{GATE (2)}$  to J6. Enable the power supplies and verify the voltage readings on the respective pins are -4.0 Vdc.

- 3. Connect V<sub>DRAIN (1)</sub> to J3 and V<sub>DRAIN (2)</sub> to J4. Enable the +28 Vdc power supply. The DUT should not draw current.

- Slowly lower the voltage connected to V<sub>GATE (1)</sub> until the drain current in the first stage transistor (Q1) is roughly 100 110 mA.

- Slowly lower the voltage connected to V<sub>GATE (2)</sub> until the drain current in the final/output stage (Q2 & Q3) is 200 -220 mA. If using a single power supply for the drain voltages, the total quiescent current should be 300 - 330 mA.

- 6. To shut down the amplifier, first ensure an RF input signal is not present and either reduce both gate voltages (i.e. more negative) effectively lowering the DC current draw to zero, or remove / toggle OFF the drain voltage(s). The second option maintains the gate voltages at the proper settings for the quiescent current should the drain voltages be reapplied.

Rev Date: 2/11/2014